# 1. 研究課題・受託者・研究開発期間・研究開発予算

◆研究開発課題名 単原子長ゲートによる低環境負荷物質から成る高出力THz帯増幅器の創出

◆受託者 国立大学法人広島大学

国立大学法人東北大学、国立研究開発法人産業技術総合研究所、国立大学法人東京大学、国立大学法人筑波大学、

◆研究開発期間 令和4年度~令和6年度(3年間)

◆研究開発予算(契約額) 令和4年度から令和6年度までの総額273百万円(令和6年度97百万円)

## 2. 研究開発の目標

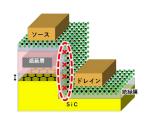

本研究開発では、SiC基板上に成長させた低環境負荷材料であるグラフェンの厚みを長さとした単原子長ゲートに、ゲート絶縁膜を介して、 二次元半導体を接合させることで、低環境負荷物質から成るTHzトランジスタの実現を目指す。

### 3. 研究開発の成果

究

目

# 1. 単原子長ゲート

グラフェンを用いて、ゲート長が単原子レベルまで 短縮した単原子長ゲートを創出

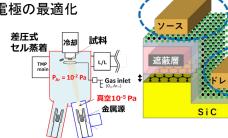

1-a SiC基板へのグラフェン成長

1-b SiC基板上グラフェンの微細加工

1-c グラフェン端の化学結合状態の 観察

# 2. 二次元半導体縦型トランジスタのチャネルおよびゲート・スタック

トランジスタを構成する各材料の配置構造とその構築プロセスをゲート絶縁膜と 二次元半導体との界面特性、二次元半導体の品質・特性に着目して、最終目標 達成を図る。

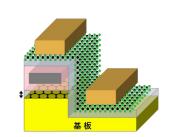

2-a 想定素子構造の検討

2-b 原子層堆積法によるゲート絶縁膜 の成膜条件と膜特性の検討

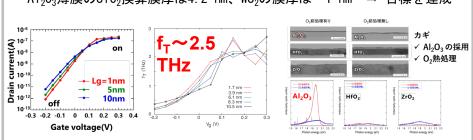

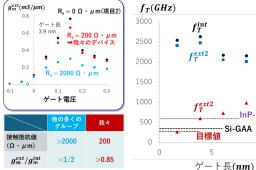

2-c ゲート絶縁膜上への二次元半導体 の位置選択的三次元成長法の検討 研究成果2-a ✓非平衡グリーン関数法とポアソン方程式を用い、極短 ゲート・トランジスタをモデル化し、スイッチング動作を確認。更に、本 トランジスタの遮断周波数が~2.5 THzに達することを示した。

研究成果2-b /高誘電率ゲート絶縁膜へのWSz成膜前のOz熱処理により、 成膜したWS。の結晶性が向上することを確認

研究成果2-c ✓単原子長ゲート上へ原子層 (ALD) 堆積法によりAl<sub>2</sub>O<sub>3</sub> ゲート絶縁膜を形成し、さらに、その上にWS<sub>2</sub>薄膜を形成することに成功 Al<sub>2</sub>O<sub>2</sub>薄膜のSiO<sub>2</sub>換算膜厚は4.2 nm、WS<sub>2</sub>の膜厚は~1 nm → 目標を達成

### 3. 研究開発の成果

# 3. ソース/ドレイン電極接触抵抗の制御

二次元半導体上への新たな金属電極形成法を創出し、接触抵抗を制御

3-a ダメージレス金属電極堆積手法の確立

3-b 接触抵抗の評価と電極の最適化

# 4. 単原子長ゲート・トランジスタの試作および特性評価

項目1~3の成果を結集して、 二次元半導体縦型トランジスタの試作 および特性評価をおこない、 THz帯における動作可能性 を検証する。

4-a デバイス試作

目

- 4-b DC特性評価

- 4-c 高周波特性評価

### 研究成果3-a

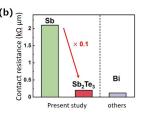

- ✓ 1Å/sでのBi堆積で表面粗さ0.3nmのダメージレス堆積を確認。

- ✓ Bi/Au極薄2層系電極により実効仕事関数を変調可能であることを確認。

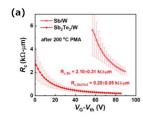

#### 研究成果3-b

✓ Y function法により接触抵抗を抽出し、BiやSb,Te,/MoS,コンタクトにおい て0.2 kΩ μ mを確認。

研究成果4-a ✓単原子長ゲート上へのAl<sub>2</sub>O<sub>3</sub>超薄膜(SiO<sub>2</sub>換算膜厚:4.2 nm) の形成、および、その上へのWS。薄膜(最小で~1 nm)を形成することに成功 ✓新たな要素技術を創出し、寄生抵抗・寄生容量を従来の1/10に低減

研究成果4-b / 項目2で得られた電気特性の理論計算に、最小化された 寄生抵抗・寄生容量を取り込んで、DC特性・高周波特性を計算し、二次元半 導体縦型トランジスタがTHz帯で高出力・低消費電力で動作することを示した

研究成果4-c ✓項目2で得られた電気特性の理論計算に、最小化された 寄生抵抗・寄生容量を取り込んで、DC特性・高周波特性を計算し、本トランジスタ がTHz帯において、既存のデバイスに比して一桁以上高出力・低消費電力で動作 することが明らかとなった。これらの特性は、Beyond 5Gに資するものである。

→先尖部の厚み「~1 nm」

寄生容量を一桁以上低減!

→遮蔽層に由来する

Si-GAA

### 3. 研究開発の成果

究

開

目

## 5. 界面準位の研究

界面欠陥の素性を明らかにし、トラジスタの高速スイッチング 特性に及ぼす影響を抽出する。デバイスモデルに組み込む。

•5-a 物理的計測による界面状態・端面状態の研究

: 超高速応答の評価

・5-b 電気的計測による界面準位の研究

: 界面欠陥密度測定の高感度化

### 6. デバイス・モデリング

回路シミュレーションでの実行に堪えるモデルであることを実証する。

6-a デバイス・モデルの構築

実証過程にて明らかとなったモデル上の弱点を是正する

6-b デバイス・モデルの実証

電気特性に対するモデル特性合わせこみ事例を拡充する。 回路シミュレーションの安定実効に資する数値的挙動を 実証する。

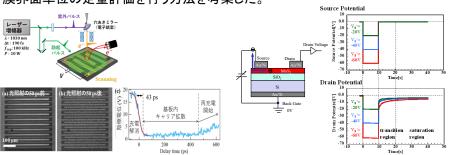

研究成果5-a ✓ 走査電子顕微鏡法(SEM)とフェムト秒レーザーを組み合わせた時間分解SEM装置を開発した。本装置により、試料表面の電位分布変化を10ピコ秒程度の時間分解能、<100nmの空間分解能で評価することが可能。研究成果5-b ✓ 膜の法線方向に空乏層が広がらない単層2次元材料と絶縁膜界面準位の定量評価を行う方法を考案した。

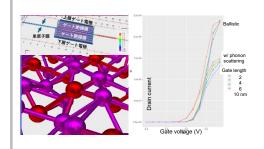

研究成果6-a  $\checkmark$ 原子レベル手法によるデバイスシミュレーションが $MoS_2$ 極薄膜MOSFET構造に於いて散乱機構を自己無撞着に含む手法にて実行可能になった。

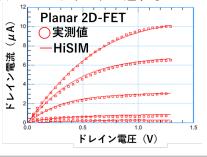

研究成果6-b ✓コンパクトモデル (HiSIM) を用いて、プレーナー型の2D半導体・トランジスタの実測値を再現することに成功! ⇒2D半導体トランジスタ・次世代LSIのモデリングに適する!

### 4. 特許出願、論文発表等、及びトピックス

| 国内出願 | 外国出願 | 研究論文 | その他研究発表 | 標準化提案 | プレスリリース<br>報道 | 展示会 | 受賞•表彰 |

|------|------|------|---------|-------|---------------|-----|-------|

| 2    | 4    | 17   | 120     | 33    | 0             | 0   | 6     |

| (0)  | (4)  | (10) | (51)    | (12)  | (0)           | (0) | (0)   |

### (1)標準化提案

※成果数は累計件数、()内は当該年度の件数です。

回路を構成する素子の挙動を、あらゆるElectronic Design Automationツール上、主に回路シミュレータ上で同じようにシミュレーションできることを企図して、回路シミュレーション用素子モデル(コンパクトモデル)の標準化が行われている。コンパクト・デバイスモデルの標準化は、国際標準化団体であるCMCを通じて行われている。広島大学は、CMCを通じた継続的な国際標準化活動を実施しており、国際標準モデルとして、極薄膜素子モデルである「SOI MOSFET用 HiSIM\_SOI」「Thin BOX MOSFET用 HiSIM\_SOTB」など5個が認定されている。これは、人的・物的資源面で圧倒的なUniversity of California, Berkleyに、比類する地位を占めている。

本課題において、広島大学(HiSIM)はMOSFETとしての基本動作は2D半導体であっても同じとの大局的な見地から、既存の極薄膜素子モデル (HiSIM\_SOIおよびSOTB)の中で2D半導体FETのシミュレーション機能の実現を目指している。既存標準モデルへの機能追加により、学理・研究だけ に留まらず、ユーザーが事業遂行可能なモデルを実現する。極薄膜素子モデルの今日の改善は2D半導体FETモデルの実現につながることを実証した。 以上のような背景の下、本課題において、広島大学から累計33件標準化提案がなされた。これらの標準化提案件数は、当初の最終目標(1件)を上回るものであり、大幅に上回った。

### (2)特許

本研究において中核となる単原子長ゲートを用いたトランジスタおよびそのアナログ集積回路応用について、特許出願を国内で2件、国外で4件行い、目標値を上回った。

### (3)受賞

本研究で取り扱う二次元半導体に関する研究に関し、応用物理学会奨励賞をはじめとする6件を受賞した。

### 5. 研究開発成果の展開・普及等に向けた計画・展望

- (1. 知財化マップ作成) 本課題以前の2021年に出願した特許および2023年6月に出願した特許について、知財化マップを作成した。その結果、次のことが明らかとなった。

- ・これらの特許は、世界的にユニークであることが認められた。

- ・米国衛星通信大手Viasat社も同様の特許を考えていたようだが、我々の特許出願は彼らに先んじることができた。

- (2. 研究開発成果の展開) 上述の知財化マップを受け、社会実装協力者と、単原子長ゲート・トランジスタ・GaN-HEMT・グラフェンアンテナのモノリシック集積デバイスの社会実装に向けた取り組みを2023年度から開始した。NICTとの連携も進めており、更なる研究開発の加速化を図っている。

- (3. 研究開発成果の普及) 社会実装協力者との共同研究開発に加えて、某自動車メーカーとEV・電動化関連で共同研究開発を開始することになった。某社が 大手メーカーであることを踏まえると、本課題の成果がこの共同研究開発を通して活用されれば、大きな社会的インパクトや国民的利益につながる。

- (4. 標準化)広島大学発のHiSIMの2D半導体トランジスタ・次世代集積回路における国際標準化を推進し、Beyond 5Gのみならず半導体分野における国際競争力の挽回に貢献していきたい。

以上、我々は、**材料~デバイス~最終製品までのレイヤー縦断的な産官学連携**を構築し、研究成果の社会実装を2030年頃に実現させるべく今後も研究開発を継続・加速化する。