# II-3. システム機器 (3)再生相関部

高橋冨士信\* 河野 宣之\*

# DECODING AND CORRELATION SYSTEM FOR VLBI

Ву

# Fujinobu TAKAHASHI and Nobuyuki KAWANO

#### 1. まえがき

最近の半導体及び磁性体デバイスの著しい進歩は、科学技術の全般的分野に大きな影響を及ぼしているが、電波干渉計技術もその例に漏れず大きな影響を受けている。従来、アナログ法しか実現できなかった相関部分は、特に、高速・高集積論理素子によってディジタル法にとって代られようとしている。今回の再生相関システムでは、この傾向を積極的に取り入れて開発してきた。本章では、VLBIデータを記録するVTRと、データを再生する再生相関部及び電子計算機NEAC3100とのインターフェースについて詳細に報告する。

### 2. VLBI再生相関システムの構成

今回開発したシステムでは、VTRに記録するまでのプロセスは、既に海外で行われている本格的なNRAOの Mark II の 手法と同様であるが、VTR記録の再生から相関までの操作では、バッファメモリとしてRA Mを用いた、オフラインの相関処理をする 方法 をとった。

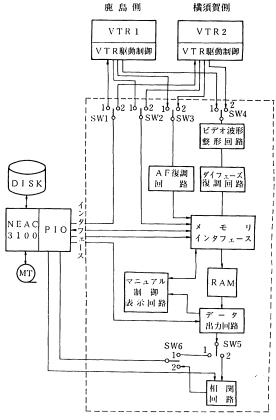

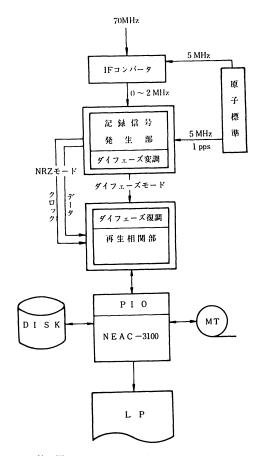

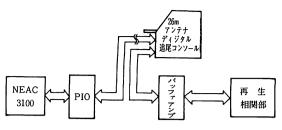

第1図に、本システムのブロック図を示す。各部の詳細な説明は、次節以降に述べることとして、ここでは処理方法の概略を説明する。

処理は大きく二つのプロセスに分けられる。第1段階では、鹿島側のVTRデータの処理を行う。第1段階では第1図のSW1~6は全て"1"側にセットされる。計算機の命令により、VTR1がPLAYし、オーディオ信号とビデオ信号がそれぞれSW3とSW4を経て、再生相関部に取り込まれる。ダイフェーズ化されたビデオ信号は、波形整形回路で波形のなまりを整形され、ダイフェーズ復調回路でNRZ信号に変換される。NRZ信

号はメモリーインターフェースで、オーディオ信号とタイミングを調整されてRAMの中に取り込まれる。

オーディオ信号はやはりダイフェーズ復調された後、メモリインタフェースを経てRAMに取り込まれる。利用者は相関をとるべきデータの時刻をマニュアル制御表示回路から設定することができる。つまり、RAMに入ったデータの時刻符号が、利用者の設定した時刻符号と一致するとRAMの内容は保存され、データ出力回路を経て計算機に格納される。以上が第1段階である。

第1図 VTR再生相関部ブロックダイヤグラム

<sup>\*</sup>鹿島支所 第三宇宙通信研究室

次の第2段階、つまり横須賀側の処理では、 $SW1\sim6$ の全スイッチを2側に set する。第1段階と同様なプロセスでRAMに取り込まれたデータは、時刻符号が設定値に一致すると相関処理に移る。第1段階で取り込んだ鹿島側データとの相関をとりながら、相関結果を計算機の磁気テープ装置に記録してゆく。相関処理はハードでもソフトでも可能である。

以上述べたプロセスでは、VTRドロップアウトについて触れていない。ドロップアウトについては本章, 6. で説明する。

# 3. データ復調整形部

## 3.1 VTR出力信号の波形整形

データを記録するVTRとして TOAMCO-VR 489 DR 一を使用した。COVTRは,第1表に示すような特性をもっている(2)。今回の実験のために,特にビデオ

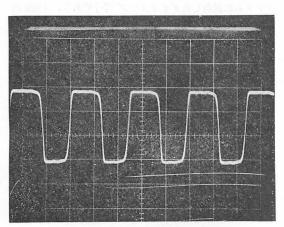

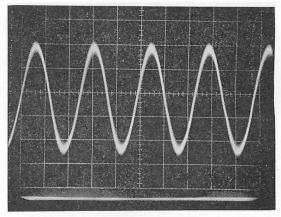

2 MHz 入力波形 200 n sec/div

2 MHz 出力波形(200 n sec/div) 第 3 図(a) 2 MHz 入力によるVTR入出力波形の比較

### 第1表 VR489DR の特性

ビデオ周波数帯域

10 kHz~6 MHz

オーディオ周波数帯域

70 Hz~10 kHz

ワウフラッタ

0.3%以下 rms

同期

複号同期,外部同期,キャプスタンサーボ

制御

リモートコントロール可能

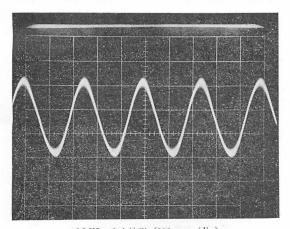

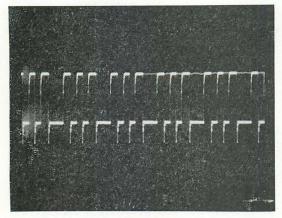

4 MHz 入力波形 (100 n sec/div)

4 MHz 出力波形(100 n sec/div) 第 3 図(b) 4 MHz 入力によるVTR入出力波形の比較

程度のリップルは止むを得ないとした。このリップルが データの位相ひずみを生み出して、VTR再生時のドロ ップアウトの原因になっていることも考えられる(本章 6. 参照)。

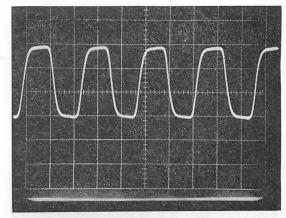

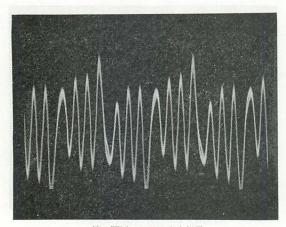

第 4 図(a) 混合波形入力

第4図(b) VTR出力信号

波形整形信号 第4図(c) 混合波形によるVTR入出力波形の比較

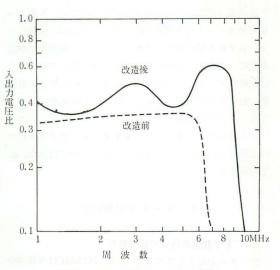

第2図 VR. 489-DR 周波数特性

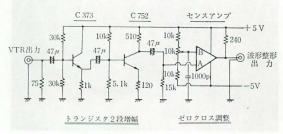

VTRに記録するデータは、2MHzと4MHzの矩形波が ランダムに混合したダイフェーズ 信号である。4 MHz の 3倍高調波が通らない9MHzの帯域幅では、通過に伴う 波形ひずみは、かなり大きなものになる。第3図は、2 MHzと4 MHzの矩形波について、VTRに記録する波形と その再生波形の比較をしている。2MHz, 4MHzいづれも 高調波成分が失われて,正弦波に近くなっている。単一 周期の単純な波形の場合には, 矩形波に整形するのは非 常に簡単であるが、ダイフェーズ信号のような不規則な 矩形波列の場合には, 再生波形は, 第4図(b)のように位 相振幅両方ともに 規則性を失うので整形は容易で はな い。第5図に、正確で微妙な波形整形調整をするための 回路を示した(3)。トランジスタ2段で十分に増幅したの ちセンスアンプでゼロクロスレベルの調整をする。その 結果,第4図(c)のような出力波形が得られる。同図(a)の 入力波形と比較すると、矩形波の duty ratio が ±10% 程度(±30 n sec 程度)変化していることがわかる。こ れ以上の改善はアナログ的には困難であるので、3.2 ダ イフェーズデータの復調回路でディジタル的に解決して いる。

第5図 VTR出力の波形整形回路(3)

#### 3.2 ダイフェーズデータの復調回路

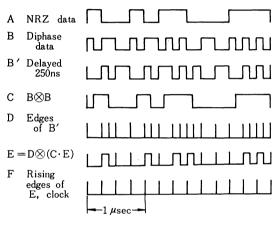

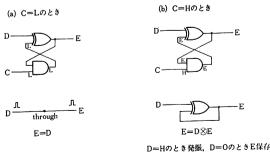

第6図に、NRZデータの変復調の原理を模式的に示す $^{(1)}$ 。 $^{(1)}$  のNRZデータをダイフェーズ変調すると  $^{(2)}$  になる。つまり、NRZがLレベルのときにはビットの立ち上りで遷移させる。また、Hレベルのときには、ビットの立ち上りとビットの中央で遷移させる。これはパルス幅変調の一種である。この変調データを復調するために遅延検波を行っている。例えば、第6図  $^{(2)}$  の信号を1ビット250 n sec だけ遅らせた  $^{(2)}$  の信号を作り、 $^{(3)}$  と  $^{(4)}$  の 排他論理和の否定をとる。すると、 $^{(5)}$  のように、元のNRZデータに比べて半ビット遅れたNRZデータが復調できる。ただし、VTRの再生信号に は本

第6図 ダイフェーズ変復調模式図

第7図 ダイフェーズ復調回路

2 11.7 0 0 74....

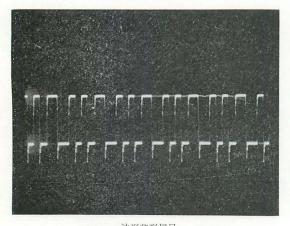

第8図 ダイフェーズ復調回路の動作

章、3.1 で述べたパルスの duty ratio の変動があるために、C のデータには、 $40\sim50$  n sec の幅をもつ「ひげ」がビットの端に立つことがある。この「ひげ」はデータ復調を誤らせる原因となるので、C のデータを積分回路に入れて「ひげ」を消している。しかし、この積分回路は、必要な信号波形もなまらせるので、C のビット列をビットの中央で正確にサンプルできるクロックパルスを再生する必要がある。このクロックの発生方法は、次のとおりである。

- (1) *B'* を微分回路に通し立ち上り,立ち下りを正極 性パルス *D* 列に変換する。

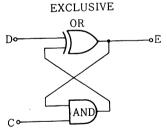

- (2) 式(1)で与えられるフィードバック論理式によって E を得る。 $\otimes$ は排他論理和,\* は論理積を示す。  $E=D\otimes(C*E)$ . .....(1)

- (3) E を微分して、立ち上り端を F 正極性パルス列 として取り出す。

以上の方法で得られたパルス列 F が、所望するクロック信号である。

(1)の論理式を、ゲートを使って表せば、第7図のようになる。これはフリップフロップの変形種と考えられる。C=0 の場合と、C=1 の場合に分けて、このフリップフロップの機能を図示したものが、第8図(a),(b)である。C=0 のときにはE=D, つまり素通り(through)状態である。C=1 のときにはE=D\*E となるので、D=1 にセットすればフリップフロップは自由発振状態になる。C,D 両信号ともに立ち上りが鋭く、ゲート内遅延が小さいときには、D のクロックパルスにより E は反転する。D=0 であれば、E は保存される。以上のことから E の信号波形を理解することができる。

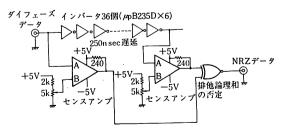

本装置では、 $B \ge B'$  の遅延量 250 n sec を TTLインバータを36個直列にして得ている。また、立ち上りを鋭くするために、必要なところにはショットキータイプのゲートを用いている。 実際の回路図を、 第9図に示す  $^{(3)}$ 。クロックによる E の 反転のレベル条件が厳しいので、排他論理和に入力する前にセンスアンプを通してレベル調整を容易にしている。

第9図 ダイフェーズデータの復調回路

#### 3.3 ビデオ信号とオーディオ信号のバランス

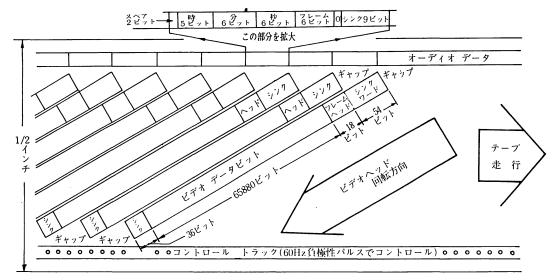

ビデオテープにデータを記録する方式として、今回のシステムでは Mark II 方式に近いビデオ、オーディオ両トラックの同時記録方式を選んだ。これは、将来の大陸間VLBIにおいて基本方式となるであろう Mark II 方式に、できるだけ近いシステムを目指すのが、今回の実験の目的の一つであったからである。第10図に、今回の我々の記録方式を図解した。オーディオトラックには、時分秒やフレームナンバ(60フレーム=1秒)から成る時刻符号を記録し、ビデオトラックには高速サンプルデータを記録する。オーディオ帯の記録速度は2 Kbits/秒であり、ビデオ帯は4 Mbits/秒である。両者ともダイフェーズ変調をかけて記録する。また、同時に原子標準に同期した60 Hz の負極性パルスを記録し、再生時のサーボ同期のタイミングとして利用している。

ビデオデータ、オーディオデータの両方ともにフレームの先頭にシンクワードを置いて、再生時に両者が独立にフレーム同期をとれるようにしている。これは、今回使用したVR-489DRのキャプスタンサーボ系が、テープ走行時の微振動の発生を防ぎきれないためである。この微振動は、オーディオヘッドとビデオヘッド間のテープ走行時間に変動をもたらし、両データ間に  $2\sim3$  m secの時間のずれを引き起こす。したがって、一方のフレーム同期によって、もう一方のトラックのデータの同期をかけることは非常に困難である。

ビデオ、オーディオそれぞれ独立に同期がかけられる場合でも、両データ間の時間のずれはデータ再生を困難にする。この場合には、ビデオヘッドのコントロールトラックに対する回転位相のトラッキングを行うことによ

って、半ば試行錯誤的に最適位置を決めながらデータを 収得してゆく必要がある。

今回の再生相関部作成にあたって、最も難しかったのが、このオーディオとビデオのバランスの問題であった。このバランスの安定度がシステム全体の安定度を決定したといえる。したがって、安定な装置系を作るためには、サーボ系の高度なVTRを使用することが望ましいことが明らかになった。

### 4. 相 関 処 理

#### 4.1 ワイヤメモリ

VTRから読み出したデータを、一時記憶させるRA Mとしてワイヤメモリ (HS-600E) を使用している。第 2 表に、このメモリの電気的仕様を示す $^{(4)}$ 。このワイヤメモリを使用した理由は、データを処理する計算機-NEAC-3100が、18ビットワードマシンであるため、

第2表 HS-600Eの電気的性能

| 記 憶 素 子    | 織成型電着磁性線<br>非破壞読出型記憶(NDRO)  |

|------------|-----------------------------|

| 記 憶 容 量    | 4 Kワード 18ビット                |

| サイクル時間     | 書込サイクル時間 600ns              |

|            | 読出サイクル時間 600ns              |

| アクセス時間     | 300ns                       |

| アクセス・モード   | ランダム・アクセス                   |

| インターフェイス・レ | vベル TTL負論理                  |

|            | "0"+2.4~+4.5V               |

|            | "1" $0 \sim +0.5 \text{ V}$ |

第10図 VTRの記録状態

メモリもワードが18ビットである方が都合が良い点と,サイクルタイムが十分高速である点を考慮したためである。このメモリはRAMとしてもROMとしても使用できるが、本装置ではRAMとして使用している。

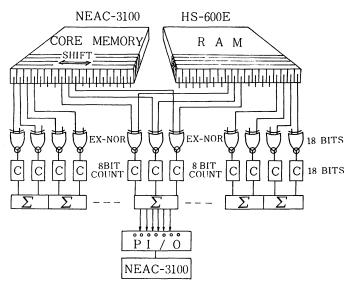

### 4.2 コアとRAMを用いた相関

2. で述べたように、相関はハード的にもソフト的にも、どちらでも行うことができる。ハード的な相関について、その処理方法を図解にしたものを、第11図に示す。

6. で説明するメインルーチンの流れに従って、鹿島側の1フレーム分のビット列を記憶したNEAC一3100のコアメモリーと、横須賀側のビット列を記憶したRAMとの間で相関計算をする。相関は排他論理 和 の 否定(第11図の Ex-NOR)のゲートを用いて行う。第11図に示すように、コアメモリもRAMも1ワード(18ビット)パラレルに処理する。Ex-NOR の各出力データは、8ビットのバイナリカウンタで積分された後、1ワード分の積分をして、その値をPIOを経由してNEAC一3100に取り込む方式をとっている。

一般に 2 組の n 個のデータ  $(x_i, i=1, n)$ ,  $(y_i, i=1, n)$  の相関値は、r 次式で与えられる<sup>(5)</sup>。

$$r = \frac{\sum_{i=1}^{n} (x_i - \bar{x}) (y_i - \bar{y})}{(n-1) S_x S_y}. \qquad \cdots (2)$$

ここで  $S_x$ ,  $S_y$  は  $x_i$ ,  $y_i$  の標準偏差であり,  $\bar{x}$ ,  $\bar{y}$  は  $x_i$ ,  $y_i$  の平均値である。今回の方式では1 ビット相関であるから,  $x_i$ ,  $y_i$  は0 と1 のランダムなビット列 である。

したがって,

$$\tilde{x} = \tilde{y} = \frac{1}{2}, \qquad \cdots (3)$$

$$S_x = S_y = \frac{1}{2} \sqrt{\frac{n}{n-1}} \qquad \cdots (4)$$

となるので、(2)式は、次のように変形できる。

$$r = \frac{4}{n} \sum_{i}^{n} \left( x_{i} - \frac{1}{2} \right) \left( y_{i} - \frac{1}{2} \right)$$

$$= \frac{4}{n} \left\{ \sum_{i}^{n} x_{i} y_{i} - \frac{1}{2} \left( \sum_{i}^{n} x_{i} + \sum_{i}^{n} y_{i} \right) + \frac{n}{4} \right\}$$

$$= \frac{4}{n} \sum_{i}^{n} x_{i} y_{i} + 1. \qquad \dots (5)$$

(5)式の第1項は $x_i$ と $y_i$ の積であり,AND(真理値表第12(a)図)に対応すべきものである。しかし,今回はEx-NOR(真理値表第12(b)図)を用いている。その理由は,Ex-NORを用いると(f)式は,更に簡単になり,かつ,相関効率が高くなるからである。

Ex-NOR の真理値表の0を-1と読み替えると,第12(c)図のようになる。これは $x_i, y_i$ についての代数的な積に等しい。この場合には,

$$\tilde{x} = \tilde{y} = 0,$$

.....(6)

$$S_x = S_y = \sqrt{\frac{n}{n-1}} \qquad \cdots (7)$$

となるので、(2)式は、さらに簡単になる。

$$r = \frac{\sum_{i=1}^{n} x_i \ y_i}{n}. \qquad \qquad \cdots (8)$$

(5)式と(8)式を比較すればわかるように, Ex-NOR を使用した方が, 相関の効率が 4 倍になり, かつ, オフセッ

第11図 相関積分回路の模式図

| $x_i$ $y_i$ | 0   | 1 | $x_i$ $y_i$ | 0   | 1 |   | $x_i$ $y_i$ | -1  | 1  |

|-------------|-----|---|-------------|-----|---|---|-------------|-----|----|

| 0           | 0   | 0 | 0           | 1   | 0 |   | -1          | 1   | -1 |

| 1           | 0   | 1 | 1           | 0   | 1 |   | 1           | -1  | 1  |

|             | (a) |   |             | (b) |   | • |             | (c) |    |

第12図 1ビット相関の真理値表

ト量を省略することができる。

### 5. オペレーションモード

4 MHzという高速度で、かつ、 66000 bits という大量 のディジタル信号の相関処理が必要であるため、次に述べるような二つのチェックモードで動作を1段階ずつ確認しながら装置の開発を進めた。

第1のチェックポイントは、4 MHz の高速データを記録信号発生部から直接再生相関部のRAMに取り込めるかどうかという点である。NEAC—3100 には DMA (direct memory access) 機能が無いので、特にこのチェックが重要である。第2のチェックポイントは、ダイフェーズ変復調が正常に動作するかどうかという点である。本章 3. で述べたとおり、特にダイフェーズ復調回路のゼロクロス条件が厳しいので、定期的なチェックが必要である。第1のチェックモードをNRZモード、第2チェックモードをダイフェーズモードと呼んでいる。

### 5.1 NR Zモード

このモードは、最もシンプルな構成によって、特にメモリ、マルチプレクサ関係のチェックをするためのモードである。第13図に、NRZモードとダイフェーズモードとの関係を示す。両モードともにVTRを経由せずに記録信号発生部と再生相関部が直接結ばれている。そして、ダイフェーズ変復調回路をバイパスしているモードがNRZモードであり、ダイフェーズ変復調を行っているモードがダイフェーズモードである。チェックはNEAC一3100のラインプリンタにビット配列を打ち出して行う。この目的のために便利なサブルーチンBITLPOの機能については、本章 6. で説明する。また、コンピュータを接続しなくても、内蔵の機能によって同様のチェックをすることが可能である。このコンピュータ代替機能は、NEAC一3100に対応する計算機の無い工場においてシステムチェックをする上で大変に役立った。

# 5.2 ダイフェーズモード

NRZモードのチェックが良好であれば、次にダイフ

第13図 NRZモードとダイフェーズモード

ェーズモードのチェックを行う。接続は、第13図のとおりである。NR スモードでは、データラインのほかに、データをサンプルする タイミングパルス 4 MHz が必要であるが、ダイフェーズモードでは、データラインにサンプルクロックの情報が入っているので、ダイフェーズデータの一系統の接続のみで動作させることができる。

VTRを経由した動作のチェックのためにダイフェーズモードでは、接続経路に低域戸波器を入れたり、イコライザアンプを入れたりして、VTRの動作状態のシミュレーションチェックを行うことも可能である。

# 5.3 本動作プログラムモード

本動作、つまり、VTRの記録再生を含めて相関処理をするモードを、プログラムモードと呼ぶ。プログラムモードの場合にはVTRのジッタや帯域の狭さ等により、非常に厳しい条件の中でデータの再生をしなければならない。5.1、5.2 で述べた二つのチェックモードをVLBPRO利用しながら、次節で述べる再生相関用ソフトウェアを有効に使用して、確実な相関処理を可能にしている。

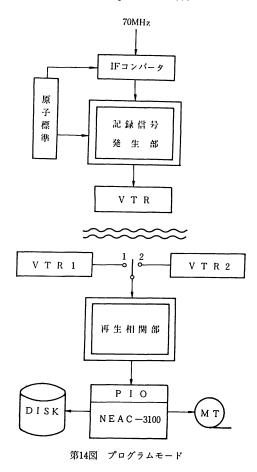

第14図に、プログラムモード時の装置の接続方法を示す。 鹿島・横須賀両局において、記録信号発生部の出力をVTRに記録して、実験終了後、両方のVTRを鹿島に集めて再生相関部による相関処理をした後、NEAC —3100の磁気テープ装置や、DISK装置に相関値を収納する。

# 6. 再生相関用ソフトウェアの構成

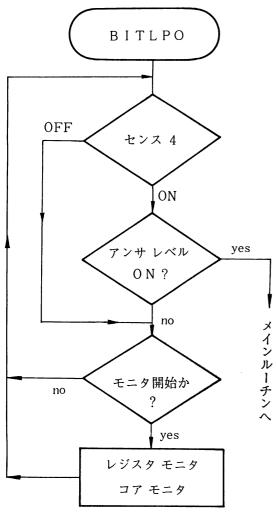

再生相関部ソフトウェア VLBPRO は、メインルーチンとビット配列チェック用サブルーチン BITLPO から

構成される。メインルーチンは再生相関部をコントロールしたり、データのやりとりの制御を行う。サブルーチン BITLPO は、メインルーチンの重要なポイントにおいて、コア内のビット配列のチェックと、使用するレジスタ数のモニタを行う。

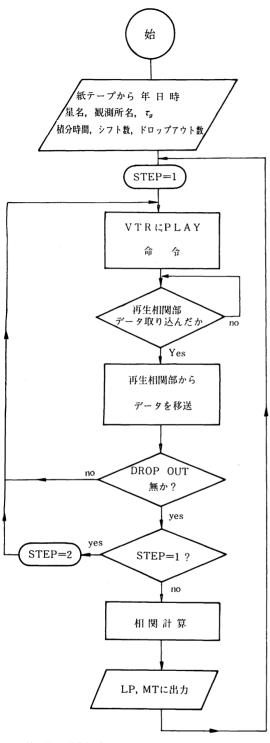

#### 6.1 メインルーチン

メインルーチンの粗フローチャートを, 第15図に示 す。最初に、紙テープから相関処理に必要なパラメータ と識別符号を読み込む(紙テープから入力すべきデータ については、第3表の説明を参照のこと。)。次に、変数 STEPを1に set する。これは第1段階, つまり, 鹿 島側のデータ処理を開始することを意味する。鹿島側の VTRにPLAY命令がかかり、VTR上の1フレーム 分のデータがRAMに書き込まれる。再生相関部では, 使用者が指定した時刻と一致するかどうか比較し、一致 するまでRAMの内容を書き改めてゆく。時刻の一致を 確認すると再生相関部は、RAMの内容を保存し計算機 にアンサを返す。アンサループで待機していた計算機 は、RAMのデータをコアメモリへ移送する。66,000ビ ットの大量の情報であるので、命令と応答を繰り返して 正確に移し終える。コアに入ったデータはドロップアウ トチェックがなされ、良好であれば次の ステップ に 進 み、ドロップアウトがあった場合には、VTRのPLA Yと命令に戻って同じプロセスを繰り返し、ドロップア ウトチェックが良好になるまで続ける。次に、変数ST EPを2に set する。つまり、横須賀側のVTRデータ の処理となる。処理プロセスは第1段階と全く同様であ る。ドロップアウトチェックが終了すると、次に相関処 理となる。相関処理はソフト的にもハード的にも可能で ある。相関積分時間やビットシフト量は任意に変えるこ とができるが、通常は積分時間を 450μ sec, ビットシフ ト量は±36ビットとしている。相関値はラインプリンタ と磁気テープに出力している。

第3表 紙テープから入力するパラメータ

|          | パラッ | v — 9 |    | 機                       | 能                  |

|----------|-----|-------|----|-------------------------|--------------------|

| ,        | τ   | g     |    | 伝搬経路の長さの养<br>単位で表す。     | その予測値をワード          |

| 積        | 分   | 時     | m  | 相関データを積分す               | ~る時間(ワード単位)        |

| シ        | フ   | ٢     | 数  | τgの予測値を中心。<br>ワード数      | に前後にシフトする          |

| ドロップアウト数 |     |       | 卜数 | ドロップアウト チ.<br>け出すリミットワー | ェック ルーチンを抜<br>- ド数 |

第15図 VLBPRO メインルーチン フローチャート

### 6.2 ビットチェック用サブルーチン BITLPO

VLBPRO のメインルーチンの中で、再生相関部から のアンサを待っている期間中に、ビットチェック用サブ ルーチン BITLPO を利用できる。これは、ドロップアウトをチェックし、システルをセットアップするのに大いに役立つ機能である。

BITLPO には、次の三つの機能がある。

### (1) 各種レジスタのモニタ機能

BITLPO は、第4表に示す8種のレジスタの内容をモニタすることができる。SCはメインプログラムからアンサルーチンに移った番地を示しており、BITLPOのリターンの番地にも対応する。ANSはアンサルーチンのレベルを示している。メインプログラムでは、 $0\sim6$ の7種のアンサレベルを用意しており、BITLPOの利用者は、SCとANSから、サブルーチンのリンク状態やPI/O や再生相関部の状態を正しくつかむことができる。第5表は、7種のアンサレベルの機能について整理したものである。

第4表 BITLPO のモニタ レジスタ

| レジスタ名 | 機            | 能          |

|-------|--------------|------------|

| S C   | アンサルーチンのもど   | り番地        |

| ANS   | アンサレベル (第5表  | 参照)        |

| X1    | メイン ルーチン カウン | 19         |

| X2    | ドロップアウト ルーチ  | ン カウンタ     |

| Х3    | 読み込ワード カウンタ  |            |

| X4    | 積分回数カウンタ     |            |

| X5    | ビット シフト カウンタ | 2          |

| DN    | ドロップ アウト リミッ | , <i>9</i> |

|       |              |            |

第5表 VLBPROのアンサ レベル

| アンサレベル | 機                | 能 |

|--------|------------------|---|

| A0     | cpu RUN WAIT の制御 |   |

| A1     | VTR サーボ同期 ONOFF  | ` |

| A2     | RAM データ取り込み終了    |   |

| A3     | RAM データ cpu 移送準備 |   |

| A4     | cpu データ相関器出力準備   |   |

| A5     | 相関終了             |   |

| A6     | 1フレーム終了          |   |

### (2) 受動 wait と強制 wait

メインルーチンから BITLPO サブルーチンに 入る と、指定したアンサレベルがONかOFFかで、次の動 作が決まる。OFFの場合には wait 状態となり、モニ タ機能を受け付ける状態になる。これを受動 wait と呼 ぶ。また、これよりも優先度の高い強制 wait も用いる

第16図 wait 状態のフローチャート

ことが可能である。センスSWの4をONにしておけば、BITLPO ルーチンに入ると直ちに wait 状態に入る。そしてモニタ機能を受け付けることが可能である。 受動 wait の場合には、NEAC-3100コンソールパネルの Base チャンネルのランプが点灯するので、強制wait と容易に区別できる。wait 状態の優先度を決める部分のフローチャートを、第16図に示す。

### (3) コアモニタ作業

コアモニタの目的は、コア内のビット配列状態が指定 どおりかどうか、プログラムシークェンスに誤りは無い かどうかを正確に識別するためである。(2)で述べた、強 制又は受動 wait 状態において、センスSWの選択により3種のコアモニタを走らせることができる。このコアモニタの特徴は、2進ビット表現でアコの内容を明示できることであり、通常の8進や16進表現に比べて直観的

第6表 VLBPRO センス スイッチ表

|     |     | センス ス | 打ち出しワード数 |    |             |

|-----|-----|-------|----------|----|-------------|

|     | 1   | 2     | 3        | 4  | 1191107 190 |

| (1) | OFF | OFF   | OFF      | ON | wait        |

| (2) | ON  | OFF   | OFF      | ON | 30ワード       |

| (3) | ON  | ON    | OFF      | ON | 300ワード      |

| (4) | ON  | OFF   | ON       | ON | 3200ワード     |

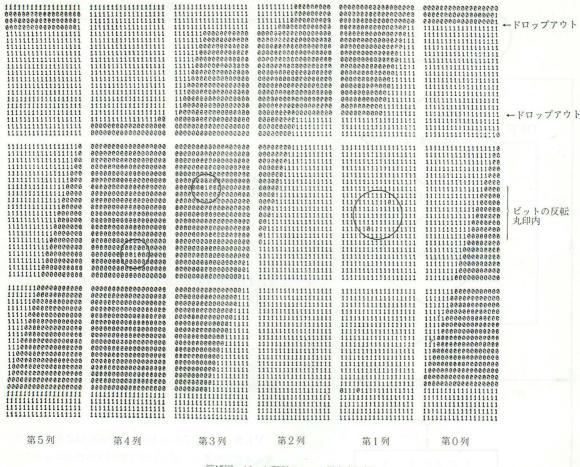

で非常に見やすくなっている。第6表に整理してあるとおり、センス1をONの場合には30ワード、センス2と1をONにすれば300ワード、そしてセンス3と1をONにすれば3200ワード、つまり、1フレーム全ビットの打ち出しが可能である。第17図に、300ワード打ち出しの例を示す。右から0列、1列、…、5列まで6列に、縦に並んでいる。この列のうち、0列と5列は同じ内容で、1行だけずらして印刷してある。これは、4列と0列のデータのつながりを知るのに、4列のつながる0列ワードを5列にとれば、ビット検査が大変楽になるためである。右端の4けたの数字は、第0列の先頭からのワード数を示す。この図では、一番下の行の一番右のワードが先頭ワードである。したがって、この図の打ち出しでは0000から0300までの301ワードのコアの内容がわかる。

VLBIにおけるビット誤りの許容性は2種に分けて 考える必要がある。厳しい条件を課せられるビット誤り としてはビットの"抜け", つまり、ドロップアウトがあ る。このドロップアウトに対しては許容性は0である。 つまり、VLBIでは1ビットでも抜ければ相関は全く 有用性を失う。一方、ビットの反転に対する許容性はか なり緩やかである。我々は、1ワード18ビット内で2ビ ットまでのビットの反転を許しているが,相関動作には, ほとんど支障は現れていない。VLBIシステムのセッ トアップを進めてきた過程は、ドロップアウトとビット 反転を区別するためのコアモニタ作業による非常に細か い作業を繰り返してきた過程とも考えられる。第17図の 例では,0000から0021までの22ワードはデータを識別 するための情報であり、0022ワード以降が相関信号であ る。この例では、22.5 μ sec の周期をもつ duty factor 50%のパルスをVTRに記録し、それを再生したもので あるので、0ビットと1ビットの斜めの帯は、それぞれ パルスのLーレベル、H-レベルを示している。この例 でも、上に述べた2種類のビット誤りが現れているが、 0208~0210ワードの区間と0282~0284ワードの区間に発 生しているドロップアウトは、10ビット以上の"ビット づまり"を引き起こしており、もしこのデータが実験の

第17図 ビット配列チェック用出力の例

観測データであれば、200ワード以上は全く相関をとることはできない。

VTRを映像再生に用いるときには多少のドロップアウトが発生しても、同期がとれておれば実用上問題はないが、相関データを記録する場合には大問題であるので十分な注意が必要である。

# 6.3 ドロップアウトの除去

これまで述べたことから、ドロップアウトをできるだけ除去して相関をとる必要性は明らかである。ドロップアウトは、本章、3.2 で述べた、クロック再生のハードの部分でクロックの"抜け"として現れるので、ハードでもフライホイル効果をもったフィルタによって、4~5ビットのクロックの"抜け"は補正している。しかし、フライホイル効果を強めて、もっと長いドロップアウトを補正しようとすると、フィルタの狭帯域化によって、今度はワウフラッタの打ち消し効果が無くなる。したがって、長いドロップアウトの除去は、ソフトウェアの方で行う必要性がでてくる。このソフトウエアには、

次の二つの条件が課せられる。

- (1) 処理時間が短いこと。

- (2) ビット反転には無関係であること。

以上の条件を満足するために、我々はハミング距離 $^{60}$ という概念を導入する。例えば、ワード $^{7}$ ルと $^{7}$ ルと $^{7}$ ルと $^{7}$ で、ハミング距離 $^{7}$   $^{7}$   $^{7}$   $^{7}$   $^{7}$

$\overrightarrow{W}_{1} = (0\ 0\ 1\ 1\ 0\ 0\ 1\ 1\ 1\ 0\ 0\ 0\ 1\ 1\ 0\ 0\ 1\ 1),$   $\overrightarrow{W}_{2} = (0\ 0\ 1\ 1\ 0\ 0\ 1\ 0\ 1\ 0\ 1\ 0\ 1\ 1\ 0\ 0\ 1\ 1),$   $D(\overrightarrow{W}_{1}, \overrightarrow{W}_{2}) = 2,$

であると考える。つまり, $\overrightarrow{W}_1$  と  $\overrightarrow{W}_2$  の二つのビット列の中の不一致ビット数がハミング距離である。VLBPROでは,ハミング距離をドロップアウトの判定 基準 として,D が 2 以下であればドロップアウトが無く,3 以上であればドロップアウトが発生しているとしている。

# 6.4 VLBPRO の規模と処理速度

VLBPRO はNEAC—3100 のアセンブラ SPASE-II  $^{(7)}$  言語で書かれている。NEAC-3100 は 26 m アンテナ追

尾用として設置したプロセスコンピュータである ため に、アセンブラの命令数や、その能力が相関処理用としては不十分である。例えば、ドロップアウトチェックに おいて、不一致ビットを調べるのに都合の良い排他論理 和の命令をもっていない。 また、 固定小数点乗除算に  $20~\mu$  sec 以上かかる。これらのことから、 VLBPRO は 約 980 ステップの大きなプログラムに なって おり、 また、その処理速度は 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7 1~7

#### 7. コンピュータコントロール

NEAC-3100と再生相関部を結ぶ制御系統図を,第18 図に示す (®)。 PIOから制御機器までのケーブル長は15 mと規定されているので,本システムでは,バッファ回路を入れてケーブル長を約30 mに延長している。 都合の良いことにPIOの外部接続端子を,26 m アンテナのプログラム追尾コンソールから全てとることができたので,第18図の系統図からわかるように,同コンソールを経由している。

第7表 PIOの入出力規格

|         |     | 入力      | 出力                     |

|---------|-----|---------|------------------------|

| 信号レベル   | "H" | +12~15V | +12~13V                |

|         | "L' | 0 ~ 1 V | 0 ~ 1 V                |

| インピーダンス | "H" | 1.7kΩ   | $1.7 \mathrm{k}\Omega$ |

|         | "L" | 100Ω    | $100\Omega$            |

|         |     |         | (許容電流 3mA以下)           |

#### 7.1 命令とそのインターフェース

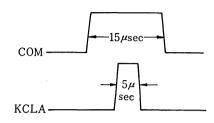

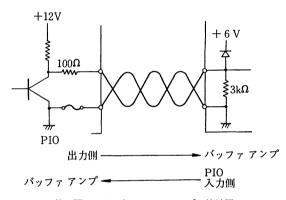

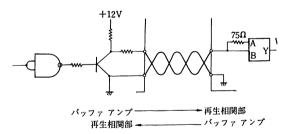

コンピュータからの命令を出力するためにPIOのDOLブロックを使用する。PIO保守説明書によれば、PIOLブロックはレベル出力回路となっているが、実際に利用するにはクリアパルスKCLAのタイミングでサンプルする必要がある。命令出力COMとクリアパルスKCLAのタイミングを、第19図に示す。命令出力のちょうど中央にクリアパルスが立っている。また、PIOとバッファアンプの接続図を、第20図に示す。PIOからの出力をON状態でSKOの抵抗で受け、SVのダイオードクランプをしている。また、バッファアンプと再生相関部との間の接続図を、第21図に示す。SV0 m の距離を引っ張って、再生相関部のSV5 のケーブルレシーバで受けている。クリアパルスKCLAも同様なレシーバで受けている。

第18図 インタフェース系統図

第19図 サンプル タイミング

第20図 PIOとバツファアンプの接続図

第21図 バツファアンプと再生相関部の接続図

けている。

#### 7.2 アンサとそのインタフェース

再生相関部の処理が正しく終了すると、計算機に対してアンサを返す。再生相関部からバッファアンプへの接続は、第21図を逆に見ればよい。再生相関部の中でトランジスタドライブしたものを、バッファアンプの中でケーブルレシーバで受ける形になる。アンサをNEAC一3100に入力するためにPIOのDILブロックを利用す

第22図 相関折れ線グラフ (100 ワード (0.45 m sec) 毎積分)

る。これは、レベル信号入力回路であり、その接続図は、第20図を逆にすればよい。

### 7.3 相関データの記録

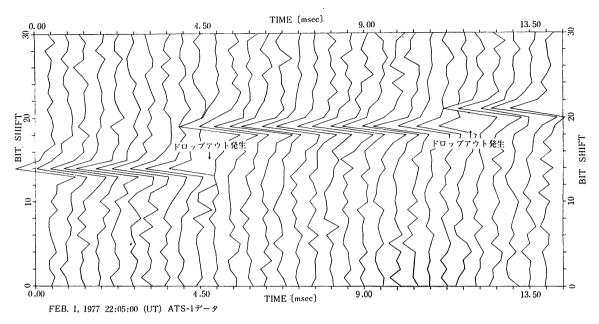

相関データは、ラインプリンタと磁気テープに出力する。第22図に、磁気テープに格納されたデータの1フレーム分をプロットしたものを示す。これはATS-1の相関データであるので、100ワード積分値を示す各折れ線のグラフにおいて、既に鋭い相関が現れている。0 m sec から 4.5 m sec までの期間では、ビットシフト14付近に負の相関が表れ、それが 4.5 m sec を過ぎると19ビット付近に移動している。これが相関係数からみたドロップアウトである。11.7 m sec 付近でもドロップアウトが起きていることがわかる。

VLBPRO では、ハミング距離の判定基準を用いて再生時のドロップアウトを少なくして、無駄の少ない相関処理を行っている。

### 8. 結 論

最低 0.3 秒の積分時間の必要な電波星 3C 273 の 相 関 検出を,本システムより成功させることができた。しかし,基礎実験用の本装置では,これ以上の長時間の積分はオペレータに大きな負担となり,実行は 困難 で あ ろ う。

次の段階としては、オフラインからリアルタイムの相 関に切り換えて、長時間の連続相関積分の可能なシステ ムを開発する必要がある。また、安定で確実な記録装置 の開発も進める必要がある。

以上のような問題点はあったが、最初の基礎実験の相 関器としてはまずまずの成果が得られた。

### 謝辞

本システムを製作するにあたり、VTRと再生相関部 インタフェース部分について、熱心に協力して頂いた日 本通信機、新井清氏及び東芝アンペックス、西村捷也氏 に深謝いたします。

## 参考文献

- (1) Clark, B. G., Weimer, R. and Weinreb, S.; "THE MARK II VLB SYSTEM", NRAO 電子工学 部門內部報告 118, 1972.

- (2) TOAMCO VR 489 パンフレット。

- (3) 日本通信機,再生相関部完成図面,波研仕5014号, 1976.

- (4) 東光, ワイヤメモリ HS-600 E, パンフレット。

- (5) P.G. ホーエル著, 浅井晃・村上正康共訳, 初等統計学, 培風館, 昭45.2.

- (6) 宮川洋,岩垂好裕,今井秀樹,符号理論,コンピュータ基礎講座 18, pp. 15-16,昭晃堂,1973.

- (7) NEC, NEAC—3100 SPASE-II 説明書.

- (8) NEC, NEAC-3100 プロセス制御装置説明書.