## 4-2-3 超高速電子デバイス技術～シリコン CMOS 高周波集積回路技術～

### 4-2-3 Ultra-high-speed Electronic Device Technology - Silicon CMOS Integrated Circuit Technology

原 紳介 笠松 章史

HARA Shinsuke and KASAMATSU Akifumi

本稿では、Beyond 5G / 6G 等に向けた sub-THz 帯無線通信技術の実現に向けたシリコン (Si) CMOS による高周波集積回路技術について概説する。基本となる高周波回路技術について、伝送線路、MOSFET を代表とする受動・能動素子について触れ、付随される寄生成分の影響について述べる。さらにこの技術を応用した sub-THz 帯無線受信機の開発例を紹介する。

This paper outlines radio-frequency (RF) integrated circuit technology based on Si CMOS process for sub-THz band wireless communication towards beyond 5G / 6G. The basic RF CMOS circuit technology, including active and passive devices such as MOSFETs and transmission line, respectively, is discussed, and the influence of accompanying parasitic components is also argued. In addition, a 300 GHz-band receiver developed using these technologies is presented.

#### 1 まえがき

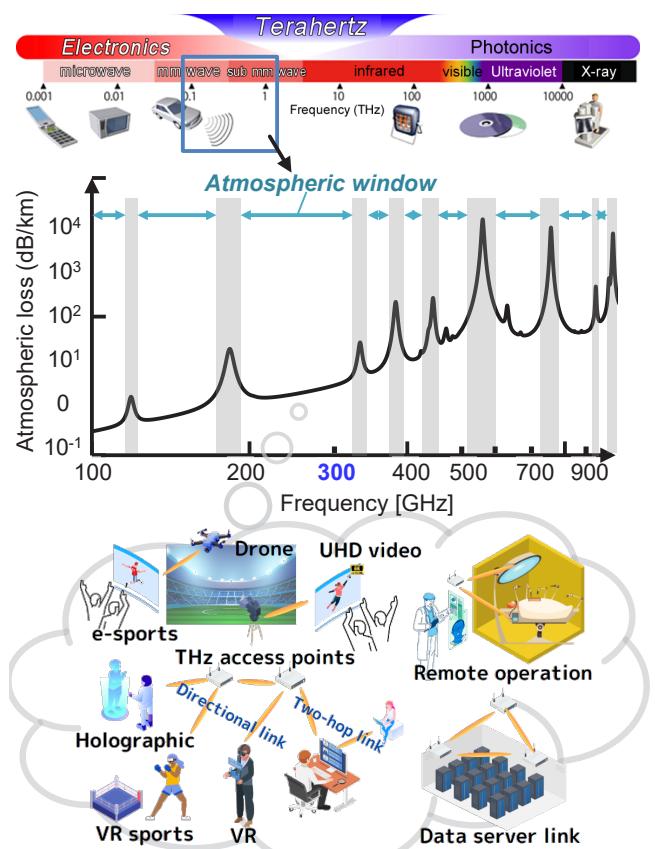

近年普及しつつある第5世代移動通信システム (5G) よりも高度な通信インフラとして、周波数 100 GHz 以上の大気減衰の少ない sub-THz 周波数帯を利用した、次世代の無線通信規格「Beyond 5G / 6G」の実現が期待されており、その基盤技術の開発が活発化している。もしこの帯域で無線通信用途に幅広い周波数が割り当てられて利用が始まれば、周波数資源の枯渇によって生じる通信容量不足の解消とともに、ICT 技術による産業構造の変革を加速させる超高速無線通信技術が確立できると予想される [1]。この期待の下、sub-THz 周波数帯の一つである 300 GHz 帯に関しては、国際電気通信連合の無線通信部門 (ITU-R) で無線通信規格割り当ての議論が進み、252 ~ 325 GHz の約 70 GHz の帯域を利用した 100 Gb/s の無線通信を目指す規格 IEEE 802.15.3d も定められた [2][3]。

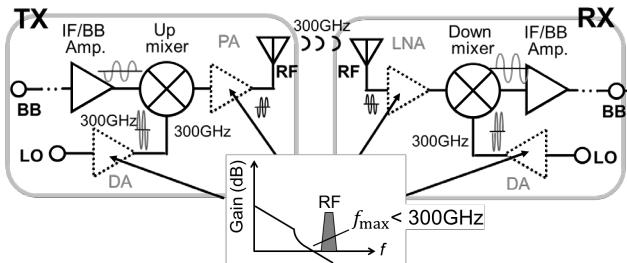

sub-THz 帯無線通信技術を確立するうえで、情報を高周波信号に変えて送信アンテナに送り出す送信機、発信された電波を受信して必要に応じて情報を取り出すための受信機の開発が必要になる。RF フロントエンドと呼ばれるこれら回路は、増幅器や周波数混合器 (ミキサ)、発振器などにより構成され (図 2)、能動素子 (トランジスタ、ダイオードなど) や受動素子 (伝送線路、抵抗、キャパシタ、インダクタなど) を单一の半導体基板上に一体化した RF モノリシックマイクロ

波集積回路 (MMIC) として実現されている。

図 1 100 GHz ~ 1 THz の大気減衰率 [4] と sub-THz 帯無線通信の応用例

図2 従来の無線送受信機アーキテクチャと、 $f_{max}$ がキャリア周波数以下の際に生じる課題

表1 半導体技術の比較

|      | III-V | SiGe | CMOS |

|------|-------|------|------|

| 高速性  | ☺     | ☺or☺ | ☺    |

| 出力電力 | ☺     | ☺or☺ | ☺    |

| 消費電力 | ☺     | ☺or☺ | ☺    |

| 集積度  | ☹     | ☺    | ☺    |

| コスト  | ☹     | ☺    | ☺    |

| TAT* | ☺?    | ☺    | ☺    |

\*Turn Around Time

この設計する上で、無線信号を送受信する搬送波（キャリア）の周波数帯でのトランジスタの性能が、システムの性能に直接影響する。代表的に利用されるテクノロジー（半導体技術）としては、III-V族化合物半導体（InP、GaNなど）、歪技術を応用したシリコンゲルマニウム（SiGe）、シリコンCMOS技術が挙げられ、この特徴を表1にまとめる。トランジスタの高速性は、電流利得遮断周波数（ $f_T$ ）及び最大発振周波数（ $f_{max}$ ）により表される。III-V族化合物半導体やSiGeはその材料特性により優れた高周波特性を有しており、sub-THz帯無線通信回路のテクノロジーとして適しているといえる。一方でシリコンCMOSは、高度な微細化技術と安定的な大量生産が可能である点から集積度・コスト・TATが格段に優れている。また他のデジタル計算処理やメモリ回路と集積・一体化することも可能であるため、広く一般普及させるためには、RFフロントエンドもシリコンCMOSによって作られることが理想的である。しかしながら、微細化技術により向上してきた高周波特性は、寄生要素の増大が原因で  $f_{max} \approx 300\text{ GHz}$  程度を境に減少傾向にある[5]。

一般的に、 $f_{max}$ より高い周波数帯域では信号増幅ができず、高い利得・出力の増幅器を実現するためには、動作周波数よりも約2倍以上高い $f_{max}$ が求められる。このため $f_{max}$ が300GHz程度のCMOSでは、アンテナと直接接続するパワーアンプ（PA）と低雑音増幅器（LNA）が、sub-THz帯域の300GHz帯では設計できない。広い帯域が未活用として残っている300GHz帯

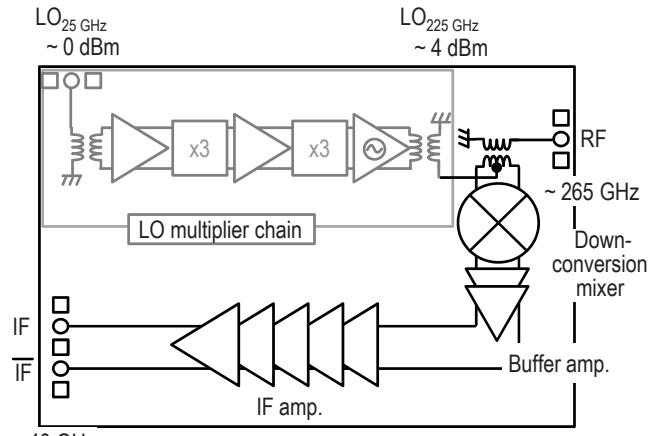

図3 高周波集積回路の例（300 GHz 帯受信機回路のブロック図）

の無線送受信機（トランシーバ）の開発をCMOSで行う場合、PA、LNAを含まないアーキテクチャによる回路技術が必要となる。

この課題解決に向けて、シリコンCMOSを利用して300GHz帯の無線送受信機集積回路を開発してきた。次節では、この研究の一部についてシリコンCMOS高周波回路技術の基礎を交えながら概説する。

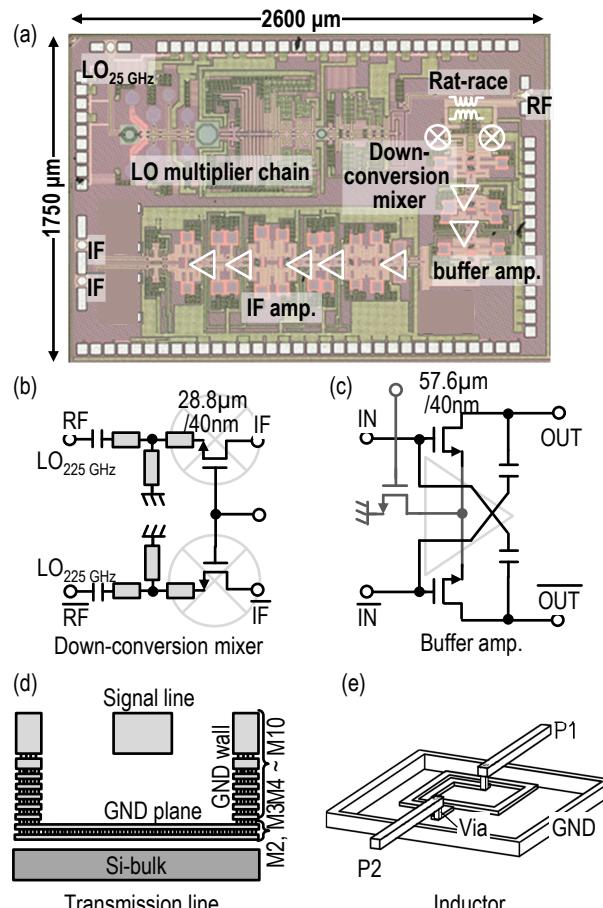

## 2 高周波集積回路

シリコンCMOS高周波集積回路の例として、図3に開発した300GHz帯受信機回路を示す[6]。先述したように、シリコンCMOSでは300GHz帯で増幅器を設計できないため、LNAレスのミキサーファーストのアーキテクチャを採用している。高周波（RF）信号を中間周波数（IF）へ変換するためのダウンコンバージョンミキサ、バッファ増幅器とIF増幅器により構成され、またチップ外部より供給される局所発振（LO）信号をミキサへ供給するために9倍するLO倍増回路群が付与されている。

高周波集積回路は図のように、様々役割を果たす回路ブロックを縦続的に接続して構成する。各ブロック単体の性能を高めつつ、ブロック間の信号伝播の効率を高めることが、設計を行う上で重要になる。特に受信機回路においては、微弱RF信号をノイズに埋もれさせないようするため雑音指数が重要な指標となる。縦続接続した場合の雑音指数（ $NF_{total}$ ）に関するフリスの式を以下に示す。

$$NF_{total} = NF_1 + \frac{NF_2 - 1}{G_1} + \dots + \frac{NF_n - 1}{G_1 \times G_2 \times \dots \times G_n} \quad (1)$$

$NF_{total}$ は各回路段の雑音指数（ $NF$ ）と利得（ $G$ ）により表され、特に初段性能（雑音指数 $NF_1$ 、利得 $G_1$ ）が重要になる。ミキサーファーストのアーキテクチャを採用

した本回路では、この初段に配置したダウンコンバージョンミキサがその役割を担うが、LNA と異なり利得はプラスにはならない。そのため初段ミキサの低雑音化と高利得(低損失)化の実現と、また後段の増幅器と効率的な接続を実現することが回路特性を向上するうえで重要になる。これを実現するには、次項に概説する高周波回路技術を駆使して設計を進める必要がある。

## 2.1 シリコン高周波回路技術 [7]

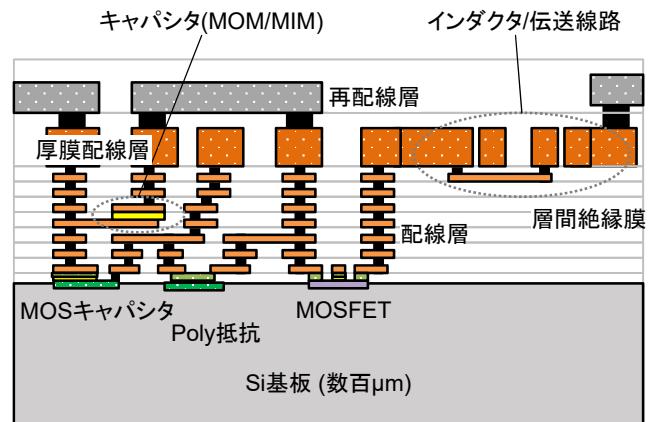

シリコン CMOS 高周波回路は、ロジック回路などに用いるものと同じ一般的な CMOS プロセス構造を利用する。シリコン基板上に形成した MOSFET などの能動素子と、信号入出力を電気的に接続するための多層配線構造より構成される(図 4)。高周波回路は、通常のベースバンド用のアナログ回路とは異なり、対象の周波数の性能が得られるように設計する。この際、トランジスタなど能動素子の性能を最大限引き出すためには入出力のインピーダンス整合が不可欠であり、その整合回路に多層配線構造を利用した伝送線路やインダクタ、キャパシタなどの受動素子を用いる。

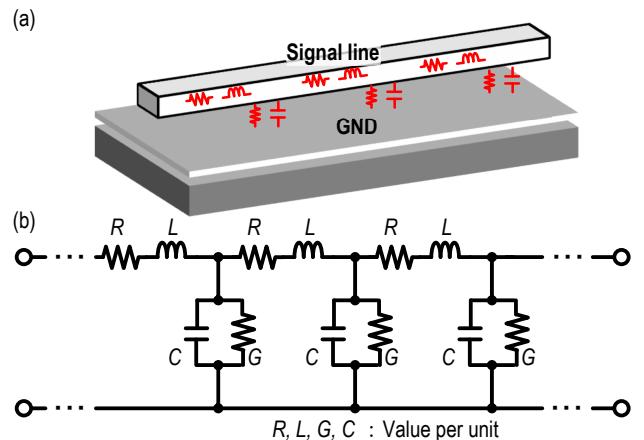

特に回路素子をつなぐ導線(伝送線路)は、低周波回路では単なる電気的な接続を役目とするが、信号の波長が線路の長さに対して無視できなくなる周波数領域では、交流電流に起因する磁界による電流の流れの抑制や隣接する導体との容量結合で電荷の移動により、インダクタンス・キャパシタンス成分を付与した分布定数の等価回路として表される。各成分により伝送線路の複素伝搬定数  $\gamma$  と特性インピーダンス  $Z_0$  は以下の式で定義される。

$$\gamma = \sqrt{(R + j\omega L)(G + j\omega C)} = \alpha + j\beta \quad (2)$$

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \quad (3)$$

一般的なシリコン CMOS プロセスでは化合物半導体とは異なり、ドーピングされた数  $m\Omega \cdot \text{cm} \sim$  数十  $\Omega \cdot \text{cm}$  程度の低抵抗基板が用いられるため、基板との誘導結合により伝送線路など受動素子は損失が大きくなる。このため、厚膜配線層や埋込再配線層を利用した信号線と、下位配線層に基板アイソレーション用の GND をセットで利用する各種伝送線路が活用される。また sub-THz 波帯の高周波回路では、伝送線路はインピーダンス整合用素子としても活用する。このため損失が少なく整合に適した減衰定数  $\alpha$ 、位相定数  $\beta$ 、特性インピーダンス  $Z_0$  を持つ伝送線路を設計し、高精度の設計モデルを構築することが、設計を行う上で鍵となる。他の代表的な受動素子としてキャパシタやインダクタが挙げられるが、伝送線路同様に周波数が

図 4 Si CMOS プロセスの多層配線構造

図 5 (a) 伝送線路と (b) その等価回路

高くなるにつれて寄生成分の影響によりその特性は変化する。受動素子はこの影響を考慮に入れて設計する必要がある。

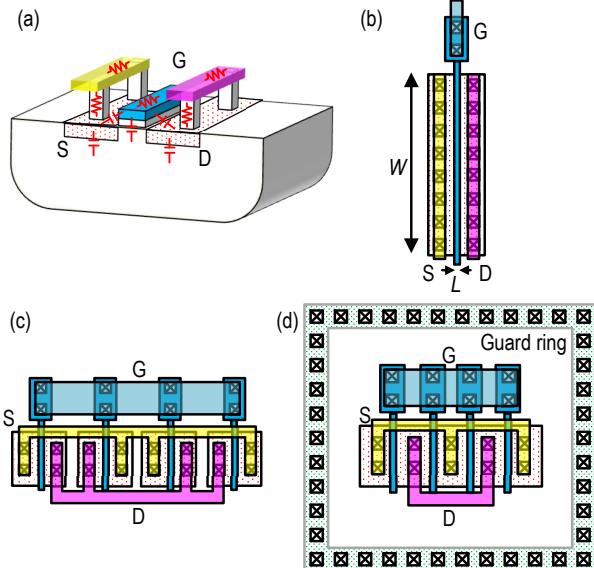

次にトランジスタの高周波設計特有の事情について概説する。トランジスタ動作させるためには各電極に配線を接続しなければならないが、この配線により真性部分のトランジスタのほかに各電極配線の抵抗成分や配線間の容量成分など複雑な寄生成分が付加される。特にゲート抵抗やゲート容量は高周波特性に悪影響を与えるため、可能な限り低減させるための工夫が必要になる。図 6 (b)～(d) は同じサイズ(ゲート長 L、ゲート幅 W) の nMOSFET のレイアウトであるが、図 6 (b) を 4 分割したものが図 6 (c)、さらにソース・ドレイン電極を共通化したものが図 6 (d) になる。それぞれの変更により、ゲート抵抗の低減と、寄生容量の低減を可能としている。高周波設計用の FET モデルは一般的に Si ファウンダリのプロセスデザインキット (PDK) により提供されるが、sub-THz 帯などでは対応できないこともあります、その場合は測定結果から独自の回路モデルを構築する必要がある。

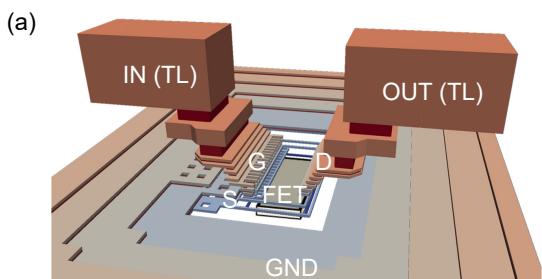

また先述したように、高周波信号の信号線は、基板

図 6 n-MOSFET の (a) 構造と (b) ~ (d) レイアウト例

図 7 (a) パンジスタと信号線路の接続と (b) その寄生成分の等価回路例

による損失を防ぐためにプロセス上位層の厚膜配線層などを利用する。この信号線からトランジスタまで電気的に接続する必要があるが、この接続配線においても寄生成分要素が存在する(図7)。周波数が高くなるにつれこの影響は顕著になるため、電磁界解析などを駆使してこの寄生要素を正しく見積り、設計に反映させることが重要となる。

## 2.2 300 GHz 帯 CMOS 無線受信機回路 [6]

先に示した 300 GHz 帯受信機回路の実際に試作したチップ写真を図 8 (a) に示す。初段配置のダウンコン

図 8 (a) 試作した 300 GHz 帯無線受信機回路のチップ写真、(b) ダウンコンバージョンミキサと (c) バッファ /IF 増幅器の回路図、(d) 伝送線路と (e) インダクタの構造図

バージョンミキサにゲート接地型ミキサを採用した(図 8 (b))。トランジスタと信号線の寄生抵抗を低減可能であり、また最小限のスタブのみで入力整合を取ることが可能であるため、雑音特性と損失の低減が実現できる。ダウンコンバートされた IF 信号用の増幅器には、キャパシタクロスカップリング手法を用いたコモンソース型増幅器を採用した(図 8 (c))。トランジスタのゲート-ドレイン間の寄生容量を低減させ、利得の向上が実現できる。伝送線路は GND ウォール付きマイクロストリップ線路を採用し、信号線に厚膜配線層を利用して伝搬損失の低減を実現している(図 8 (d))。またインダクタのパラメタライズセル(P-cell)を独自設計し、IF 信号の整合回路に用いることでチップ面積の小型化を実現している(図 8 (e))。 $f_{max} \approx 280$  GHz の 40 nm プロセスを使用した本回路は、上記のようなシリコン高周波回路技術を多数駆使して設計している。

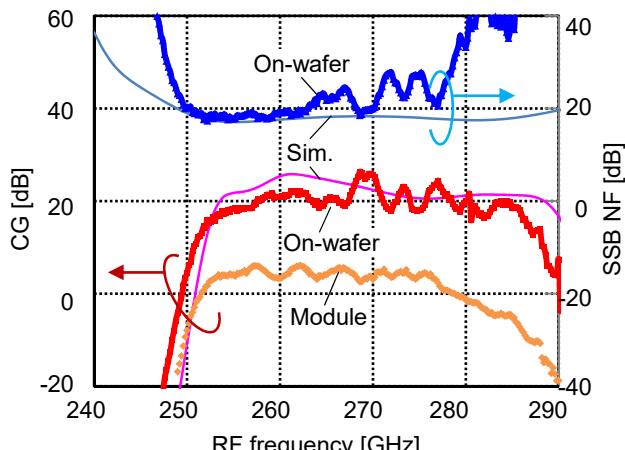

試作した CMOS 受信機の性能評価結果を図 9 に示す。測定・評価は NICT ネットワーク研究所 先端 ICT デバイスラボ(ミリ波研究棟)の共用設備であるマニュアルプローバ及びネットワークアナライザなどを用

図9 試作 300 GHz 帯無線受信機の周波数特性

いて実施した。高周波プローブを用いたオンウェハ測定の結果、出力特性として、26 dB の変換利得 (CG)、17.4 dB の雑音指数が得られた。

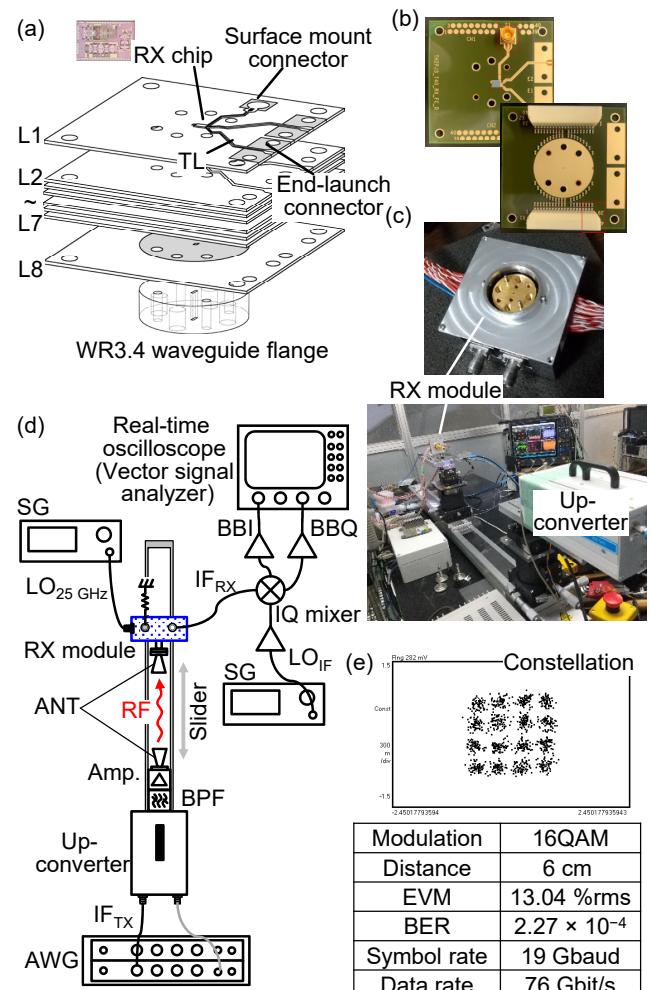

試作した受信機回路を、導波管変換機構を備えた PCB 基板上にフリップチップ実装することでモジュール化し(図 10 (a)–(c))、無線伝送実験を実施した。試作した受信機モジュールの通信性能を、市販されている 300 GHz 帯アップコンバータと 26 dBi のホーンアンテナ、各種測定機器を利用して評価した(図 10 (d))。この結果、16 QAM 变調信号を用いた無線伝送において、最大 76 Gbit/s のデータレートが得られた(図 10 (e))。

### 3 まとめ

Beyond 5G / 6G の取組は既にスタートしており、そのロードマップが総務省「Beyond 5G 推進戦略懇談会」により策定された[8]。Beyond 5G / 6G の機能として、「超高速・大容量」、「超低遅延」を具備することが求められており、sub-THz 帯無線通信はこれらを実現するための要素技術の候補の一つにあたる。本稿では sub-THz 帯無線通信技術の基盤技術を担うと考えられるシリコン CMOS 高周波回路技術について概説し、その応用例として 300 GHz 帯無線受信機の開発について紹介した。今後、送受信機の性能の向上と共に、実用化に向けた更なる開発が期待される。

### 謝辞

本研究は総務省「電波資源拡大のための研究開発 (JPJ000254)」の一環として行われました。研究の実施にあたり助言をいただいたプロジェクトメンバーに感謝いたします。

図10 (a) モジュール用 PCB 基板の構造図、(b) 基板と (c) モジュール写真、(d) 無線実験セットアップ、(e) 無線実験結果

### 【参考文献】

- 1 G. Ducournau, P. Sriftgiser, F. Pavanello, E. Peytavit, M. Zaknoune, D. Bacquet, A. Beck, T. Akalin, J.-F. Lampin, and J.-F. Lampin, "THz communications using photonics and electronic devices: The race to data-rate," *Journal of Infrared, Millimeter, and Terahertz Waves*, vol.36, no.2, pp.198–220, Feb. 2015.

doi: 10.1007/s10762-014-0112-x

- 2 Final Acts WRC-19. Accessed: July 12, 2022. [Online].

<http://handle.itu.int/11.1002/pub/813b5921-en>

- 3 IEEE Standard for High Data Rate Wireless Multi-Media Networks-Amendment 2: 100 Gb/s Wireless Switched Point-to-Point Physical Layer, IEEE Standard 802.15.3d-2017, 2017.

- 4 AMATERASU. Accessed: July 12, 2022.

<https://smiles-p6.nict.go.jp/thz/jp/decay.html>

- 5 H.-J. Lee, S. Rami, S. Ravikumar, V. Neeli, K. Phoa, B. Sell, and Y. Zhang, "Intel 22nm FinFET (22FFL) Process Technology for RF and mm Wave Applications and Circuit Design Optimization for FinFET Technology," 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2018, pp.14.1.1–14.1.4.

doi: 10.1109/IEDM.2018.8614490

- 6 S. Hara, R. Dong, S. Lee, K. Takano, N. Toshida, A. Kasamatsu, K. Sakakibara, T. Yoshida, S. Amakawa, and M. Fujishima, "A 76-Gbit/s 265-GHz CMOS Receiver With WR-3.4 Waveguide Interface," *IEEE Journal of Solid-State Circuits*, vol.57, no.10, pp.2988–2998, Oct. 2022., doi: 10.1109/JSSC.2022.3179560

- 7 浅田邦博, 松澤昭, “アナログ RF CMOS 集積回路設計 応用編,” 培風館, 2011.

- 8 総務省, “Beyond 5G 推進戦略 – 6G へのロードマップ –,” 2020.

URL: [https://www.soumu.go.jp/main\\_content/000696613.pdf](https://www.soumu.go.jp/main_content/000696613.pdf)

## 4 百折不撓・デバイス研究

原 紳介 (はら しんすけ)

未来 ICT 研究所

小金井フロンティア研究センター

超高周波 ICT 研究室

主任研究員

博士 (理学)

高周波集積回路、ナノ電子デバイス

【受賞歴】

2018 年 IEICE 論文賞

2017 年 RFIT2017 学会賞受賞

2015 年 RFIT2015 学会賞受賞

笠松 章史 (かさまつ あきふみ)

未来 ICT 研究所

小金井フロンティア研究センター

研究センター長

博士 (工学)

高周波電子デバイス・システム

【受賞歴】

2023 年 令和 5 年度情報通信月間推進協議会

会長表彰 志田林三郎賞

2019 年 第 64 回 (平成 30 年度) 前島密賞

2017 年 第 28 回電波功績賞 電波産業会代表

理事表彰