Newly developed technology

- Mixed-signal architecture realizes ultra-high-speed data transmission, improving power efficiency

The research group has developed the world's first mixed-signal baseband demodulator circuit consisting of a high-speed, low-resolution ADC and a small-scale DSP. This technology is expected to realize higher-data communications exceeding tens of Gb/s, achieving a superior power-efficient baseband demodulator circuit.

In general baseband demodulation circuits in high-speed wireless communications consist of a high-speed, high-resolution ADC and a large-scale DSP and, if used for such high-speed communications, the required performance of ADC and DSP results in extremely distorting power efficiency. The developed technology solves these problems. - The receiver circuits with the baseband demodulator enables 20Gb/s QPSK data transmission

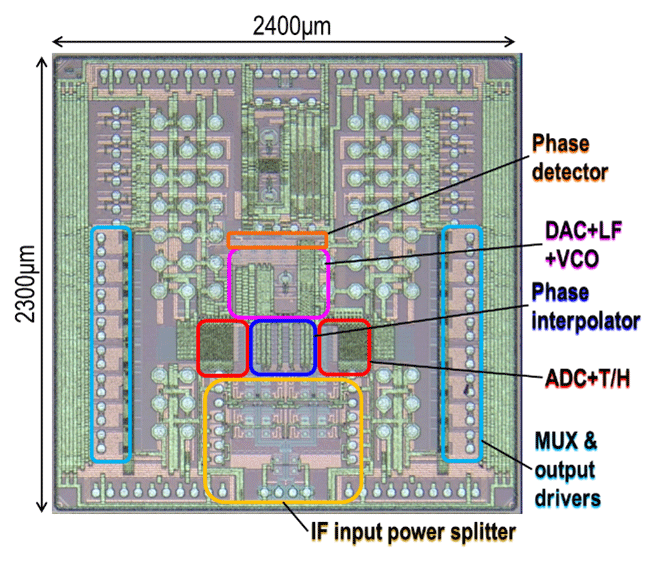

The developed receiver circuits the baseband demodulator and an FPGA with logic circuits have achieved data transmission of 20Gb/s QPSK modulated signals. The functions implemented in FPGAs will be integrated into baseband receiver circuits in its practical application. - Outline of the achieved circuits

The achieved technology simplifies the circuits by making the carrier frequency an integer multiple of the symbol carrier frequency, achieving ultra-high-speed data transmission by a unique circuit configuration with a mixed-signal QPSK Costas loop that integrates carrier, timing, and data recovery functions. The research group has achieved the high-speed, low-resolution ADC by implementing an 8-way interleaved 3-bit ADC (8x speed-up as the total circuits) with the sampling rate of 40-gigasample-per-second (40GS/s) and recovered data with the FPGA.

Background of the MIC R&D Project

Reference

1THine Electronics, Inc., 2National Institute of Information and Communications Technology, 3Hiroshima University

nict.go.jp

nict.go.jp